# Low Power Optimization Datasheet for Texas Instruments AM389x Sitara ARM processors

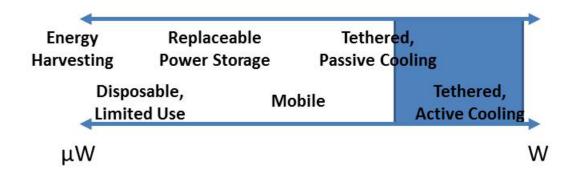

1. The AM389x Sitaraprocessors target the shaded portion of the low power spectrum.

2. Operating voltages:

0.9V, 1V AVS (SmartReflex Technology), 1V constant, 1.5V, 1.8V, 3.3V

- 3. Typical power at maximum operating frequency

- 1.2GHz ARM/1GHz DSP is 4 to 9W (depending on peripheral use and temperature)

- 4. AM389x Sitara processors include support for clock gatingfor each module on chip.

- 5. AM389x Sitara processors use three (3) power domains to support power gating. One (1) additional power domain is always on. The memory power domain supports light sleep, deep sleep, shut down modes.

- 6. AM389x Sitara processors support multiple supply voltages in the same ranges indicated in #2 (0.9V, 1V AVS (SmartReflex Technology), 1V constant, 1.5V, 1.8V, and 3.3V).

- 7. AM389x Sitara processors use Texas Instruments' Smart Reflex Technology and scaling the PLLs separately to support both voltage and frequency scaling.

## **Low Power Optimization Datasheet for**

## Texas Instruments AM389x Sitara ARM processors

- 8. AM389x Sitara processors include the following hardware accelerators:

- HDVPSS (HD Video Processing SubSystem) w/ Media Controller

- 3D Graphics (SGX530)

- ELM (Error Locator Module) accelerates NAND ECC.

- EDMA

- 9. AM389x Sitara processors do not support multithreading or hardware context switching.

- 10. Multicore processing is a standard capability for AM389x Sitara processors via the ARM Cortex-A8 core with NEON and hardware mailbox and spinlocks.

- 11. Additional information for:

- A. Making your code faster:

- The AM389x Sitara is an ARM Cortex-A8-based processor with dedicated support for control, connectivity, and GUI functions. The ARM core can run at top speeds of up to 1.5GHz. TI offers industry-standard APIs that can offload media processing tasks that tend to be the heaviest loads on the system.

- The AM389x Sitara also uses a NEON vector floating-point engine and a

dedicated graphics processor. The compiler tools allow easy speed-up of the code

that can use the vector FP capabilities of Neon. The media portions of the

application can use industry standard OpenMax and OpenGL APIs to speed up

processing.

- B. Using the hardware accelerators

- The AM389x Sitara supports dedicated HW acceleration for graphics.3D graphics is offloaded into dedicated 2D/3D graphics engines that provide OpenGL and OpenVG acceleration.

- C. No additional information for sleep and idle modes

- D. Optimize the locality of memory

- The AM389x Sitara features advanced capabilities that organize local memory to maximize the throughput of the memory sub-system.

- The advanced dedicated HW systems can organize the normal raster memory into tiles that are extremely efficient for data management and transfer.

## **Low Power Optimization Datasheet for**

## Texas Instruments AM389x Sitara ARM processors

• The advanced dynamic memory manager HW module can organize, prioritize and re-order memory transactions in a manner that maximizes the utilization of the memory throughput.

### E. Using buffers and pre-allocated resources

- The AM389x Sitara offers dynamic resource management capabilities that allow flexible allocation of HW to applications. Memory allocations can be dynamic, driven by system use-cases, and/or centrally managed by the Host operating system.

- The HW resources for media processing and signal processing can also be centrally managed by the host operating system and allocated across the various applications dynamically.

- TI's software features the Syslink driver which allows a flexible management of all the HW co-processors and the memory needed by them.

#### F. Optimize data movement

• The AM389x Sitara offers a system enhanced DMA engine with 4x controllers and 16x channels per controller that can be used flexibly by the host or one of the several co-processors if desired. Other DMA engines in the system manage the transfer of data across PCIe and Ethernet.

#### G. Optimize interrupt handling

• TI's software architecture allows offloading of interrupt handling tasks to the coprocessor engines. As an example, scaling and displaying multiple channels of HD media in the system would involve servicing many interrupts per second simply to keep the media engine going. Doing this on the host will kill its performance and leave no room for the host application or other tasks. Offloading this to a slave processor that uses a real-time operating system to service and handle the interrupts keeps the HW engines at maximum throughput.

#### H. Manage multi-threading

The AM389x is an asymmetric application engine in which media threads can be offloaded to other slave processors to free the host processor to focus on host tasks.