MIPS Technologies

M4K

Targets: Automotive, Consumer, Industrial, Mobile & Wireless

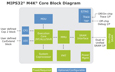

The MIPS32 M4K core is a 32-bit synthesizable core targeting embedded designs and microcontroller applications. Configurable features allow designers to optimize the core's performance while balancing die size, power consumption and total system cost.

Using a 5-stage pipeline, the M4K core offers more than 500 MHz operation and greater than 1.5 DMIPS/MHz in performance. It has a build-time configurable external SRAM interface optimized for cacheless operation, enabling increased system performance and deterministic operation. The M4K core has built-in architectural features that enable reduced power consumption without effecting the frequency or performance. CorExtend capabilities enable designers to create differentiated SoC designs by adding their own instructions.

The configurable and synthesizable core enables flexibility for designers to include only those features necessary for their application. Software and hardware tools support design and verification. MIPS16e code compression allows designers to reduce the memory requirements for their applications by as much as 40%. BIST, scan and EJTAG debug with trace (PDtrace and iFlowtrace) and fast download enable quick debugging.